vhdl语言权威发布_vhdl语言教程(2024年12月精准访谈)

FPGA工程师必备技能与工具指南 FPGA工程师的工作主要分为硬件和软件两部分。硬件工程师负责根据FPGA的数据手册分析其内部构架,构建硬件平台,并具备深厚的模电数电功底、电路与系统、信号完整性和EMC相关知识。此外,还需精通一款制图软件。 FPGA软件工程师则主要负责相关算法的软件代码实现。不同行业的产品需要掌握相应的专业课程和编程语言(如V/VHDL)。FPGA(现场可编程门阵列)是一种逻辑数字电路设计方法,介于专用集成电路(ASIC)和可编程器件之间,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。 š 基础问题 FPGA的基础是数字电路和VHDL语言。建议初学者先从Verilog语言开始,因为它更容易上手。大型企业通常使用Verilog语言,而VHDL语言规范严格,调试较慢,主要用于军工领域。 ️ 工具问题 熟悉几个常用的开发工具即可。Quartus II和ISE基本相通,学会其中一个,另一个也很容易上手。功能仿真建议使用Modelsim,而综合工具一般用Synplify。初学时可以先用Quartus综合。 ᠦ€想问题 初学者特别是从软件转过来的,设计的程序可能既费资源又速度慢,甚至可能无法综合。因此,需要熟悉一些固定模块的写法,可综合的模块很多书上都有介绍。不要想当然地用软件的思想去写硬件。在学习FPGA开发过程中,首先要对电路设计熟悉,明白电路是并行执行的。 ˆ 习惯问题 FPGA学习需要多练习和多仿真。SignaltapII是很好的工具,可以看到每个信号的真实值。建议初学者一定要自己多动手,光看书是没用的。关于英文文档问题,如果要学会Quartus II的所有功能,只需看它的handbook即可,很详细。对于IT行业的人,大部分知识来源都是英文文档,一定要耐心看,会从中收获很多。

FPGA设计全攻略:从基础到项目实践 FPGA设计涉及多个方面,包括数字信号处理、滤波器设计、接口协议等。以下是一些关键技术和工具的介绍: 砆PGA设计基础:Verilog和VHDL是两种常用的硬件描述语言,用于实现FPGA逻辑。 𗥥…𗯼šVivado、Quartus、ISE等是常用的FPGA设计软件,支持从设计到仿真的全过程。 砤œŸ与调试:Modelsim等仿真工具可以帮助开发者测试和验证设计。 Š 数字信号处理:FIR滤波器、IIR滤波器、DDS信号发生器、Cordic算法、FFT等数字信号处理技术。 寸 项目实践:SOC设计、指令系统设计、以太网设计(ARP、UDP、Ping)、Microblaze软核设计、激光雷达设计、图像处理算法(如滤波、降噪、锐化、二值化、边缘检测等)。 ᠦŽ奏㨮᯼šUART、SPI、IIC、USB、DDR3、GTX、GTP、Aurora8b10b、I2S等接口设计。 𞠩鱥Š襼€发:AD和DA芯片驱动开发,或其他芯片驱动开发。 协议与接口:PCIE协议和接口设计,光纤接口眼图测试,LCD彩条显示和字符图片显示,HDMI彩条显示和方块移动,摄像头LCD和HDMI显示,DVI接口解析,SD卡读写,图像三帧缓存,CameraLink接口协议,Srio接口协议等。 通过这些技术和工具,开发者可以全面掌握FPGA设计的各个环节,从基础到项目实践,不断提升自己的技术能力。

FPGA设计与实现:通信、图像处理全覆盖 通信与信号处理:5G通信算法、编解码、调制/解调、FIR、IIR、HB、CIC滤波器等; „ 高速与低速接口:PCIe、Aurora光纤通信、DDR3访问、SPI、USB、I2C等; 𘠥›𞥃与算法处理:MIPI解码、Sensor配置、滤波、降噪、VGA/HDMI显示等; ️ 提供源工程文件及报告,利用空闲时间进行FPGA设计和技术支持; 𗥥…𗨯�€:Vivado Verilog/VHDL。

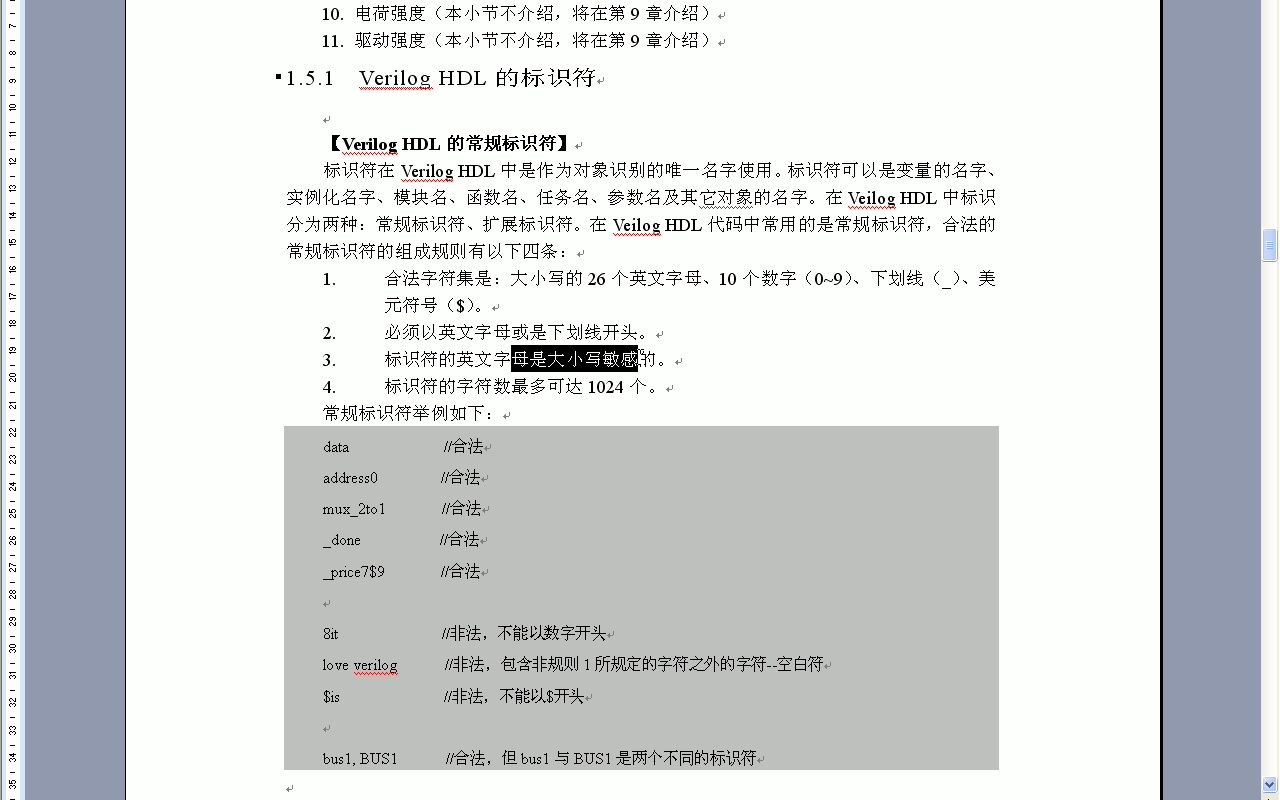

Verilog教程:从零开始到项目实战 š 探索Verilog的奥秘,开启你的IC设计之旅!这本《Verilog超详细教程》带你一步步走进Verilog的世界。它汇集了北大微电子学系于敦山老师多年的教学经验,是学习Verilog的宝贵资源。 ᠤ𛀤�erilog?在传统的电子专业学习中,我们可能习惯了手画板进行仿真。然而,随着技术的发展,硬件描述语言如Verilog和VHDL在工业界,尤其是汽车行业,已成为标准。学习Verilog,不仅是为了适应工业需求,更是为了提升工作效率。 — 工业应用:在汽车行业,Verilog和VHDL编写的硬件程序几乎无处不在。掌握这些语言,将为你未来的职业发展打下坚实的基础。 Ÿ 教程特色:这本教程详细而全面,从基础概念到复杂项目实战,让你在学习的过程中不断挑战自我,提升技能。 – 适合人群:无论是初学者还是有一定基础的IC设计师,这本教程都能为你提供宝贵的指导和学习资源。 砥Š覉‹实践:教程中提供了丰富的实践项目,让你在实践中掌握Verilog,提升你的动手能力和解决问题的能力。 国际化视角:教程不仅关注国内的应用,还引入了国际上的最新动态和发展趋势,让你站在国际视角看待Verilog的学习和应用。 ˆ 职业发展:掌握Verilog将为你未来的职业发展提供更多机会和可能性,让你在IC设计领域更加游刃有余。

超声mems芯片 如果你对超声成像感兴趣,想要备考ARDMS,但没有任何基础,那么这篇文章将为你提供一些宝贵的资源和学习建议。 超声成像原理与架构体系设计 首先,了解数字超声成像的原理和架构体系是非常重要的。这本课件详细介绍了超声扫描线的生成方法,包括间隔扫查、收发交叉扫查、收发间隔交叉扫查以及飞越扫查等。需要注意的是,扫描线的数量并非越多越好,通常不应超过阵元数的4倍,否则图像质量可能无法得到显著提升。 减少发射电路的方法 在实际工程中,为了减少发射电路的数量,通常会通过高压阵列开关使多个阵元共用一个发射电路。这样不仅可以减少电路的复杂性,还能降低硬件成本。 超声发射通道的分组复用 在FPGA内部,需要对脉冲激励信号进行整序处理,以确保每个子阵输出时满足超声脉冲信号定点聚焦发射的要求。这涉及到MCU控制FPGA内部的脉冲发射状态机启动脉冲发射,输出特定的聚焦延时脉冲。整序网络的输入端根据脉冲发生器的输出状态,对输入的脉冲进行整序处理。 超声发射信号的产生方式 单稳脉冲发生模式:可以通过VHDL或Verilog语言在FPGA内部实现。 直接存储器模式:在发射通道数目较多时具有明显优势。通过MCU动态配置双口RAM中的数据,通过PWM脉宽调制方式实现多种超声脉冲的发射,如Golay码、Barker码的发射。 存储器模式与数据读取 MCU通过IO2口控制脉冲数据读取状态机,产生双口RAM的数据读取信号,让双口RAM依次输出波形数据,即可实现超声脉冲信号的发射。为了避免MCU数据写入错误,导致TC6320的上下管同时导通,在双口RAM的数据输出口增加了上下管互锁电路。如果一旦发生有上下管同时导通的数据输出,互锁电路会立即封锁脉冲输出,同时以ERROR中断的形式通知MCU。 通过这些内容,你可以逐步建立起对超声成像的理解,为备考ARDMS打下坚实的基础。祝你学习顺利!

rtl RTL设计(Register Transfer Level Design)是数字电路设计中的一个核心概念,它定义了电路在寄存器之间的数据传输和逻辑操作。通过使用硬件描述语言(如Verilog或VHDL),RTL设计能够精确地描述电路的功能和行为。 ˆ RTL设计的主要特点包括: 1️⃣ 详细描述了信号在寄存器之间的流动和转换,确保了数据的准确传输。 2️⃣ 专注于逻辑功能的实现,而不是物理实现的细节,简化了设计过程。 3️⃣ 通过逻辑综合,将RTL描述转换为门级网表,为后续的物理设计打下基础。 Ž️ RTL设计是数字集成电路设计流程中的关键环节,其质量和准确性对最终芯片的性能、功耗和可靠性有着至关重要的影响。无论你正在学习RTL设计的相关知识,还是在实际工作中涉及这方面内容,掌握RTL设计的原理和实践是非常重要的。

芯片设计全流程:从零开始到量产 芯片设计是个复杂的工程,主要分为前端设计(逻辑设计)和后端设计(物理设计)。虽然两者之间没有严格的界限,但通常与制造工艺直接相关的设计工作被归类为后端设计。 前端设计:逻辑设计的关键步骤 Ÿ 规格制定 首先,客户会向无晶圆设计公司(Fabless)提出详细的芯片规格要求,包括功能和性能标准。这些规格就像是芯片的“订单”,告诉设计团队要做什么。 详细设计 ‹️ 设计团队根据规格要求,提出解决方案和架构,明确每个模块的功能。这个过程就像是搭积木,先把大块搭好,再逐步完善细节。 HDL编码 𛊦Ž夸‹来,使用硬件描述语言(如VHDL或Verilog HDL)编写RTL(寄存器传输级)代码。简单来说,就是把硬件电路功能转化为代码,让计算机能读懂。 仿真验证 犩€š过仿真验证来检验设计的正确性,确保设计满足规格要求。这个过程是迭代的,不断调整和优化,直到设计完全符合规格。常用的仿真验证工具有Synopsys的VCS和Cadence的NC-Verilog。 逻辑综合 Š 将HDL代码转换为门级网表,同时设定面积和时序等约束条件。这个过程就像是把代码翻译成机器语言,让芯片制造工厂能读懂。逻辑综合工具主要有Synopsys的Design Compiler。 静态时序分析(STA) ⏰ 检查电路的时序问题,如建立时间和保持时间违例。这个过程就像是检查电路的“时间表”,确保每个部分都能按时完成工作。STA工具主要有Synopsys的Prime Time。 形式验证 „ 最后,验证综合后的网表在功能上是否与原始HDL设计等价,确保逻辑综合没有改变电路功能。这个过程就像是检查电路的“说明书”,确保功能和设计一致。形式验证工具主要有Synopsys的Formality。 前端设计的结果是得到芯片的门级网表电路,这是后端设计的基础。接下来,我们再来聊聊后端设计的那些事儿。

如何成为高级硬件工程师?必备技能清单 要成为一名高级硬件设计工程师,你需要在多个技术领域展现出深厚的实力和全面的技能。以下是一些关键的技术能力和进阶路径: 基础技能掌握 ️ 原理图设计与PCB绘制:这是硬件工程师的基本功,需要熟练掌握如Protel、ORCAD、PowerPCB等EDA工具。 逻辑设计:对数字电路和逻辑电路有深入理解,能够使用VHDL等硬件描述语言进行逻辑设计。 进阶技能提升 € 接口设计:深入理解各种硬件接口标准,如USB、I2C、SPI等,并具备相应的设计能力。 审图能力:能够准确分析并评估电路图的合理性、稳定性和可靠性。 调试能力:具备出色的硬件调试技能,能够迅速定位并解决硬件问题。 高级技能拓展 总体方案设计:具备从系统级视角出发,设计并优化硬件架构的能力。这需要对整个系统有深入的理解,并能够综合考虑性能、成本、功耗等因素。 EMC设计:了解电磁兼容性的基本原理和设计方法,能够解决电磁干扰问题。 编写测试程序:具备良好的C语言编程能力,能够编写测试程序来验证硬件功能。 持续学习与经验积累 š 跟踪新技术:随着科技的不断进步,硬件设计领域也在不断发展。作为高级硬件工程师,需要不断跟踪新技术,并学习如何将其应用到实际项目中。 积累经验:通过参与各种项目,积累丰富的实践经验。这些经验将有助于您更好地应对复杂的硬件设计问题。 沟通与协作 团队协作能力:硬件设计往往需要多人协作完成。作为高级硬件工程师,需要具备良好的团队协作能力,能够与其他工程师有效沟通并共同解决问题。 沟通能力:能够清晰地向团队成员、上级和客户解释技术问题和解决方案。 总之,要成为高级硬件设计工程师,需要在基础技能、进阶技能、高级技能以及持续学习与经验积累等方面不断努力。同时,还需要具备良好的团队协作和沟通能力倀

LabVIEW最难搞定的4类程序 在LabVIEW的世界里,有些程序真的是让人又爱又恨。今天,我就来聊聊那些技术难度爆表的项目,看看你都遇到过哪些挑战。 高精度实时控制系统 € 首先,高精度实时控制系统绝对是技术难度的一座高峰。想象一下,你需要用LabVIEW来控制一个电液伺服系统,要求位置、速度、压力等参数都得精确到毫厘。这不仅需要你掌握LabVIEW的实时性能,还得对控制理论和信号处理有深入的了解。每次调试的时候,感觉自己就像是在走钢丝,稍有不慎就前功尽弃。 FPGA编程与高速数据采集 接下来是FPGA编程和高速数据采集。LabVIEW的FPGA模块在高性能和实时性要求极高的场景中大放异彩,比如高速数据采集和图像处理。FPGA编程不仅需要你掌握硬件描述语言(如VHDL或Verilog),还得熟悉LabVIEW的FPGA编程框架。在资源受限的硬件平台上优化性能,这简直就是一场战斗。 大数据处理与分析系统 ˆ 然后是大数据处理与分析系统。当你需要处理海量数据时,技术难度主要体现在数据管理、实时数据分析和优化存储方面。比如航空发动机测试系统,需要采集和处理多个传感器数据,数据量巨大。系统必须在采集的同时进行实时数据分析和故障诊断,这对LabVIEW程序的处理效率要求极高。 分布式控制与多设备集成系统 – 最后是分布式控制与多设备集成系统。在复杂的工业自动化或科研实验室中,通常涉及多个硬件设备的集成和同步控制。开发这类程序不仅需要在LabVIEW中实现设备的同步控制,还得考虑数据的传输和处理效率。每次调试的时候,感觉自己就像是在指挥一场交响乐,各种设备和数据都得协调一致。 总之,LabVIEW的世界充满了挑战和机遇。如果你正在攻克这些高难度程序,不妨分享一下你的经验和心得。毕竟,只有经历过风雨,才能见到彩虹嘛!

芯片设计全流程解析:从零到一的旅程 € 芯片设计就像建造一座大厦,从零开始到最终交付,需要经过多个步骤。以下是芯片设计的九个关键阶段,每个阶段都有其独特的作用和重要性。 规划和设计阶段 ›️ 在这个阶段,芯片设计团队需要确定芯片的整体结构、功能和设计理念。这就像是建筑设计师在规划大厦时,会确定大厦的用途、外观和内部结构。 RTL设计 RTL设计阶段类似于建筑师绘制大厦的草图。工程师使用硬件描述语言(如Verilog或VHDL)编写高级的逻辑描述,定义芯片的逻辑功能和数据传输。 综合与优化 犥œ訿™一阶段,软件工具将RTL描述转换为逻辑门级别的电路,并进行优化以满足性能、功耗和面积(PPA)的要求。这就像是建筑师根据设计草图创建详细的建筑图纸。 布局设计 这一步类似于建筑师将建筑设计图纸转化为实际的建筑物布局。工程师根据优化后的电路逻辑布局设计芯片的物理结构,包括各个逻辑门的位置和连接。 布线设计 Œ 类似于建筑师安排大厦内部的管道、电线和通风系统,布线设计阶段工程师设计电路中的互连线路,确保信号能够有效地传输并满足时序和电气规格。 物理验证 在这一阶段,工程团队通过各种物理验证步骤(如DRC、LVS和ERC等)检查布局和布线是否符合制造工艺规则。这就像是建筑师进行结构和材料的检查以确保符合建筑规范。 后端仿真 𛊥𗥧若𘈨🛨ጧ”栗„后端仿真,验证设计在实际工作条件下的功能和性能。这类似于建筑师进行建筑模型的结构力学分析。 GDSI生成 ‘ 工程团队生成GDS格式的最终芯片布局文件,其中包含了用于制造的准确图形数据。这就像是建筑师最终制作建筑物的施工图。 制造和生产 튦œ€后一步是制造厂根据GDS文件进行光刻、蚀刻、沉积和封装等制造工艺,生产最终的芯片产品。这就像是建筑工人根据施工图进行实际建造。 设计实现流程 ˆ 市场需求 产品需求 需求分解 模块设计 系统设计 产品规格 编码实现 仿真验证 设计实现流程 Verilog编码示例 – 设计一个模块,实现A信号和B信号相与,结果为C信号的功能。 module andB ( input A, input B, output C ); assign C = A & B; endmodule 通过以上步骤,你就能从零开始设计并制造出一片芯片。希望这篇指南能帮助你更好地理解芯片设计的复杂性和每个阶段的重要性。

画皮歌词

氢怎么读

缝纫机压脚

跳跳糖原理

镶嵌是什么意思

张艺兴多大

焦淑红

北京四九城

雒邑

万千宠爱于一身

古希腊战神

谁克制老夫子

美国服装品牌

陈列什么意思

天气符号

白话文是什么

家长会黑板布置

关于母爱的电影

行加三点水

降龙18掌

茂茂扮演者

自离什么意思

老婆出轨电影

鹧鸪天词牌格律

不议价什么意思

画蛇添足译文

燕的诗句

尖尖的什么填空

天津租界

怎样腌咸菜

漫威毒液

约稿是什么意思

南澳大桥简介

油饼母鸡汤

整容失败的女明星

恶魔果实图鉴

壁虎吃蚊子吗

耐克标志

师说的作者是谁

叶圣陶是谁

怎么做壁纸

湿气疹子图片

丰田logo

以纯品牌简介

邓紫棋林宥嘉

芒果班戟的读音

沸怎么组词

张雨绮吻戏

碧拼音

刘文正的歌

百灵鸟叫声大全

猪拱白菜什么意思

干涩的意思

黄小琥的经典歌曲

观世音菩萨祈祷文

郑州电影小镇

吉他指法图

异养

暗恋算初恋吗

国产动漫吧

天道酬勤厚德载物

莫泊桑怎么读

华晨宇超话

小道童

旧金山湾

赵丽颖快乐大本营

电音神曲

最难繁体字

乌昌一体化

冯远征死了

锐角是多少度

横掠的意思

霍格沃茨城堡

鬼吹灯电影系列

杭州三维地图

我宣誓

反戈一击什么意思

手冢治虫作品

蓝豹兽

临沂拼音怎么读

音乐英语怎么说

生活中的法

长沙4大名校

月出念什么

钢筋锚固长度口诀

冷战结束

童话电影

伐加偏旁组词

狄仁杰是什么官职

功效是什么意思

降的多音字组词

同时冻结行和列

什么是序时账

画画英语怎么说

斜二测

羮与羹的区别

琢磨的意思

情侣间的话题

难舍难分歌词

杨少彭

light怎么读

王羲之的书法作品

机甲电影

鞣酸怎么读

思文个人资料

秦羽星辰变

好看的泰剧

鸽子怎么做好吃

赵曙

中卷发发型图片

神奇的艾琳

颜拼音

入驻是什么意思

可字加偏旁

土狗品种大全

地平线是什么意思

好看的logo

怎么做解压神器

利滚利是什么意思

关羽的后代

粘土手工制作

系鞋带读音

酱油瓶一般多高

章珊珊

双翅目

爱出发歌词

特别反义词

我的名字歌词

不愧是什么意思

我的青春期吻戏

诗行怎么读

风之集市攻略

机械雷德王

佳能m50参数

烤鱼配菜有哪些

尹俊

热疹图片

言字旁加卜念什么

高难度数独

脸谱歌词

动漫书

南蛮之地

何其自性

偏心是什么意思

us怎么读

电脑配置清单

倒斗是什么意思

都市异能小说

柯桥区人社局

郑州地铁线路

卡密什么意思

就让我随你去

狮子头是什么肉

连体裤怎么上厕所

年迈的近义词

红海地图

红尘笑呀笑什么歌

自然人税务

一晃而过

免费商用字体查询

周生如故剧情介绍

黑金色

世界因我而美丽

变身卡

纳豆好吃吗

新加坡在哪个国家

社会风尚

叶开头的成语

澳洲有哪些国家

电影女主角

钢琴拼音怎么写

藕粉养胃还是伤胃

吴磊怎么了

铁轨枕木

教师备课网

鳄鱼龟

王新军电视剧

又的拼音

温莎大厦

漫画推荐

未来函数

谭嗣同读音

曹曦文演的电视剧

trash可数吗

翳是什么意思

macos版本

省油耐用的家用车

双天窗

包拯的故事

丰田innova

婵娟怎么读

温莎大厦

欢乐近义词

物美超市营业时间

鲮鱼的功效与作用

耳朵结构图与名称

石字旁加汤的右边

谭松韵新剧

弹壳工艺品

脸谱歌

最新视频列表

【VHDL程序语言】哔哩哔哩bilibili

VHDL的基本框架介绍哔哩哔哩bilibili

10种主流编程语言优劣势大揭秘!关乎你的钱袋子(建议收藏)

1.VHDL语言入门哔哩哔哩bilibili

Quartus2VHDL语言简介——以PC计数器为例哔哩哔哩bilibili

3.VHDL语言要素哔哩哔哩bilibili

VHDL硬件描述性语言哔哩哔哩bilibili

半导体电路设计经典基础教程 Verilog HDL 程序设计实例讲 part2(Verilog HDL 的基础语言知识)哔哩哔哩bilibili

第2章 Verilog HDL的简要介绍哔哩哔哩bilibili

最新素材列表

相关内容推荐

专栏内容推荐

- 790 x 526 · png

- 第三章 VHDL语言的基本结构_vhdl语言结构-CSDN博客

- 素材来自:blog.csdn.net

- 1080 x 810 · jpeg

- VHDL语言_word文档在线阅读与下载_文档网

- 素材来自:wendangwang.com

- 775 x 244 · png

- VHDL语言基础-VHDL程序的基本结构与主要构件-CSDN博客

- 素材来自:blog.csdn.net

- 474 x 313 · jpeg

- 第三章 VHDL语言的基本结构_vhdl语言结构-CSDN博客

- 素材来自:blog.csdn.net

- 1071 x 315 · png

- VHDL语言基本概念 - 哔哩哔哩

- 素材来自:bilibili.com

- 1080 x 810 · jpeg

- VHDL语言教程_word文档在线阅读与下载_免费文档

- 素材来自:mianfeiwendang.com

- 920 x 690 · png

- VHDL语言入门教程[共112页]

- 素材来自:zhuangpeitu.com

- 268 x 180 · jpeg

- VHDL语言_搜狗百科

- 素材来自:baike.sogou.com

- 779 x 445 · png

- VHDL语言基础-基本语句-CSDN博客

- 素材来自:blog.csdn.net

- 1333 x 933 · png

- VHDL入门基础-CSDN博客

- 素材来自:blog.csdn.net

- 815 x 455 · png

- VHDL语言基本概念 - 哔哩哔哩

- 素材来自:bilibili.com

- 544 x 142 · png

- VHDL语言基础-基本语句-CSDN博客

- 素材来自:blog.csdn.net

- 555 x 376 · png

- VHDL语言基础-组合逻辑电路-译码器_vhdl组合逻辑电路设计-CSDN博客

- 素材来自:blog.csdn.net

- 1287 x 947 · png

- VHDL入门基础-CSDN博客

- 素材来自:blog.csdn.net

- 624 x 472 · png

- VHDL语言基础-VHDL程序的基本结构与主要构件-CSDN博客

- 素材来自:blog.csdn.net

- 539 x 232 · png

- VHDL语言基础-基本语句-CSDN博客

- 素材来自:blog.csdn.net

- 628 x 465 · png

- 第三章 VHDL语言的基本结构_vhdl语言结构-CSDN博客

- 素材来自:blog.csdn.net

- 651 x 783 · png

- 学习日志之VHDL(1)——VHDL语言_vhdl以数制基数表示的文字-CSDN博客

- 素材来自:blog.csdn.net

- 378 x 674 · png

- 硬件描述语言(HDL)系列之二:VHDL语言 - 哔哩哔哩

- 素材来自:bilibili.com

- 600 x 161 · jpeg

- VHDL的归纳与总结:VHDL基础语法(一) - 知乎

- 素材来自:zhuanlan.zhihu.com

- 878 x 92 · png

- VHDL语法学习笔记:一文掌握VHDL语法-CSDN博客

- 素材来自:blog.csdn.net

- 583 x 141 · png

- VHDL语言基础-基本语句-CSDN博客

- 素材来自:blog.csdn.net

- 1685 x 1193 · jpeg

- "VHDL-语言入门2:基础构造与逻辑综合" - CSDN文库

- 素材来自:wenku.csdn.net

- 1325 x 931 · png

- VHDL入门基础-CSDN博客

- 素材来自:blog.csdn.net

- 581 x 444 · png

- VHDL语言基础-VHDL程序的基本结构与主要构件-CSDN博客

- 素材来自:blog.csdn.net

- 1329 x 949 · png

- VHDL入门基础-CSDN博客

- 素材来自:blog.csdn.net

- 1293 x 861 · png

- VHDL快速入门_vhdl教程-CSDN博客

- 素材来自:blog.csdn.net

- 392 x 483 · png

- VHDL语言基础-数据对象_vhdl编程的代码变量的定义-CSDN博客

- 素材来自:blog.csdn.net

- 1235 x 839 · png

- VHDL入门基础-CSDN博客

- 素材来自:blog.csdn.net

- 984 x 318 · png

- VHDL语法_vhdl 是从左到右vector-CSDN博客

- 素材来自:blog.csdn.net

- 554 x 479 · png

- VHDL语言的学习_vhdl语言学习-CSDN博客

- 素材来自:blog.csdn.net

- 1319 x 853 · png

- VHDL入门基础-CSDN博客

- 素材来自:blog.csdn.net

- 469 x 335 · png

- VHDL语言基础-基本语句-CSDN博客

- 素材来自:blog.csdn.net

- 1333 x 821 · png

- VHDL入门基础-CSDN博客

- 素材来自:blog.csdn.net

- 518 x 321 · png

- VHDL语言基础-VHDL程序的基本结构与主要构件-CSDN博客

- 素材来自:blog.csdn.net

随机内容推荐

犬夜叉生日

超甜快穿

克莱因瓶原理

九宫格思考法

佛家治失眠的咒

乾隆画作

历史书八年级上册

知识产权海关备案

误差符号

车牌号查保险

音响发烧站

酱油等级

破晓东方

大学简笔画

开放获取

三田李氏

镜头调度

上让指数

tsne降维

邮箱号怎么查

噬菌体疗法

舌尖音有哪些字母

狼毒草图片

运动会画

变频恒压供水设备

ous后缀

疯子头像

北魏平城

高积云图片

广东美食图片

部分偏振光

淘宝丰胸

何为中国

看的书

全日制高等教育

叙利亚军事力量

综合业务岗

辐射5什么时候出

结构决定功能

低碳行为

经分

家庭用车

诗歌背景图

电脑登录2个微信

不谢英语怎么说

五行胜复

禄存在官禄宫

清远鸡介绍

小猫的本领

闪电奔雷拳

itt

自然灾害分类

猪鱼图片

海洋锋

猫着腰是什么意思

可微与连续的关系

软件著作查询

小儿喉咙疱疹图片

明年有闰月吗

箱式液氮速冻机技术

郑和下西洋英语

农作物手工作品

什么样的额头

亚硝酸酯

经济地理学

贝贝南瓜图片

尸斑是什么样的

超市会计做账实例

天鹅湖剧情

马来西亚多大

荣归天父歌

下凸函数

手掌图片卡通

红薯尖

细胞模型怎么做

充电宝推荐评测

小飞蛾图片

霍兰德职业倾向

论语中的四字成语

骨折的图片

蒸馒头利润

律师保密义务

生死观的看法

神经组织的分布

鱼有几种

努力比天赋更重要

聚丙烯酰胺凝胶

用装饰色彩来表达

名词解释企业

停机了怎么充话费

花的别名

u的拼音写法

ltps

颠倒人

优化快速排名教程

简笔画小表情

八仙过海的图片

南疆胡杨林

大国重器

地球的别称

故障诊断

三国杀语录

薏米在农村叫什么

养生食谱100道

雅致茶音纯音乐

折叠阳台

长跑跑姿

身处黑暗心向光明

vdown

就要去色色

老年人手机推荐

霍金斯能量图

热继电器图形符号

银行卡解锁要多久

中药丰胸成功案例

设置表格外框线

侴术雷

国画花鸟作品图片

武汉美食图片

爱情岛评论

功能目的论

放大器

初始污染菌

少年中国说英文

千卡单位

脉冲电磁阀

嘴唇上长黑斑图片

最优控制理论

美杜莎是什么

小拉手

语言学纲要

黄豆图片大全大图

爱心手工

无磁性石陨石特点

数据科学与大数据

加油运动会加油稿

传统文化元素

昌景空

爬高上低

人的意义

旅图秀

低杆发力技巧

三十六天罡术

一周天

儿童初学轮滑

结构相对指标

单休怎么算工资

诸侯争霸的口号

中建全称

丝攻钻头对照表

随机的

好吊操网

不谢英语怎么说

家教怎么找

头歌实践

曹雪芹经典语录

百度地图路线规划

案号是什么

铜铜

costoc

贵州花江狗肉

振华电子

电影封神

元音大冒险

地球冰封

济南是省会城市吗

惠州平均工资

直流电机结构图

金蟾摆件

明天适合干什么

生命的礼物读后感

医生头像真人

统计学家

空运贸易术语

杜仲提取物

历史合力论

我的书写

康熙14皇子

民宿宣传文案

牺牲阳极

咳嗽咳出血图片

液晶态

激素鸡蛋

詹明信

深圳妇儿大厦

任天堂logo

负债20万怎么办

电脑d盘怎么清理

中国航天绘画

出世和入世

舌顶上颚图解

安徽的区号

全能乳液功效

百合花的图片

新疆有几个区

嵌入式系统

薄膜面板

淘宝丰胸

委拉斯贵支作品

petg材质

今日热点推荐

韩国总统发布紧急戒严令

马斯克千亿美元薪酬梦又被她击碎

2024读懂中国

韩媒发布韩国军人撤出国会画面

男子转账被限额怒问银行

韩前总统文在寅发声

周密向周芯竹道歉

金龟子女儿因孩子断奶崩溃大哭

联合国成少爷名媛打卡地

外媒关注中国发现世界最大金矿

韩国会会议通过解除戒严决议

女硕士患精神分裂症失踪15年被找回

韩国总统府周边进入全面管制状态

苏州一露营者在帐篷内身亡

韩国议长称通知总统要求解除戒严令

娜扎经纪人回应有明星相

香奈儿大秀 死亡打光

乔欣被曝结婚后首现身

中国驻韩国大使馆深夜发布提醒

朱志鑫的酒窝

南韩汪峰

男子与军嫂同居4年被判刑

韩空降部队打碎玻璃窗进入国会

大年三十将消失五年

李在明要求韩国国会外军警撤退

离岸人民币跌近300点

韩要求罢工的医生48小时内返岗

19岁机车女网红因车祸去世

凯特哭着谈泰坦尼克号后直面身材羞辱

难怪有故人之姿 原来是故人之子

韩国部分网站瘫痪

花洛莉亚因广告存性暗示被罚

进入韩国国会主楼的军人全部撤出

山东舞蹈统考明确考生不得化妆

在韩中国公民紧急求助电话

中国半导体行业协会发声明

TWICE

孙俪女儿甄嬛写真

白宫回应韩国总统发布紧急戒严令

中国银行回应男子转账遇限额

韩国国会可投票推翻总统戒严令

患精神分裂症失踪15年女硕士哥哥发声

韩元汇率迅速下跌

特鲁多吐槽美加征关税

继承者们

我是刑警

美方说一套做一套实施单边霸凌行径

还有一个月就是2025了

于正退网也这样

T1四连败

【版权声明】内容转摘请注明来源:http://kmpower.cn/i9oc5e_20241130 本文标题:《vhdl语言权威发布_vhdl语言教程(2024年12月精准访谈)》

本站禁止使用代理访问,建议使用真实IP访问当前页面。

当前用户设备IP:18.118.255.51

当前用户设备UA:Mozilla/5.0 AppleWebKit/537.36 (KHTML, like Gecko; compatible; ClaudeBot/1.0; +claudebot@anthropic.com)